鈥?/div>

Routing of all I/O to any IA or MDAC

Any IA/MDAC summed to either output ampli鏗乪r

Circuits with and without feedback possible

Routable to maintain pin location relationships

Single supply (+5V) operation

Precision voltage reference output (2.5V)

Power-down for

碌

Watt power consumption

Auto-calibration of internal offsets

Available in 28-pin PDIP or 24-pin SOIC

Recon鏗乬urable or adaptive signal conditioning

Analog front end for most A/D converters

Programmable analog signal control loops

Precision programmable gain ampli鏗乪rs

Auto-Calibration

2.5V Reference

2 PD

1 GND

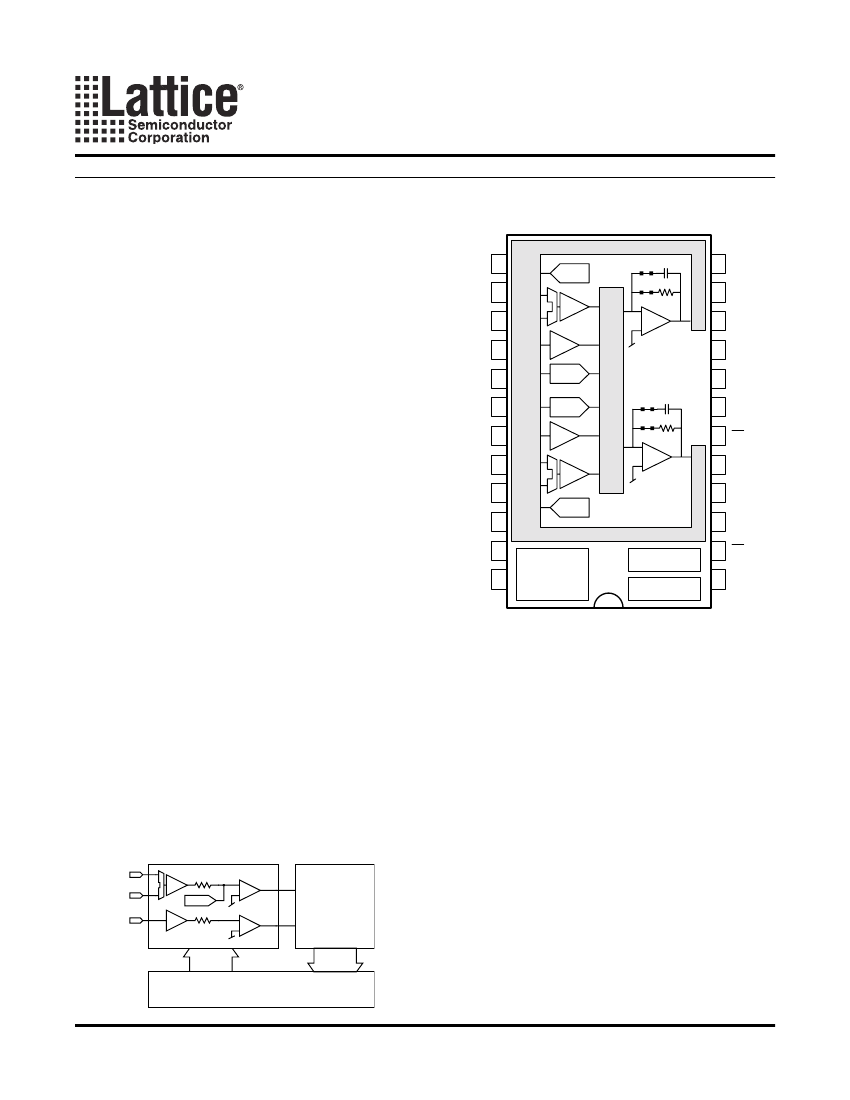

ispPAC30 24-Pin SOIC

鈻?/div>

Other Product Features

Description

The ispPAC

廬

30 is a member of the Lattice family of In-

System Programmable (ISP鈩? analog integrated cir-

cuits. It is digitally con鏗乬ured via SRAM and utilizes

E

2

CMOS memory for non-volatile storage of its con鏗乬u-

ration. The 鏗俥xibility of ISP enables programming, veri鏗?

cation and unlimited recon鏗乬uration, directly on the

printed circuit board.

The ispPAC30 is a complete front end solution for data

acquisition applications using 10 to 12-bit ADC's. It pro-

vides multiple single-ended or differential signal inputs,

multiplexing, precision gain, offset adjustment, 鏗乴tering,

and comparison functionality. It also has complete

routability of inputs or outputs to any input cell and then

from any input cell to either summing node of the two

output ampli鏗乪rs. Designers con鏗乬ure the ispPAC30

and verify its performance using PAC-Designer

廬

, an

easy to use, Microsoft Windows

廬

compatible develop-

ment tool. Device programming is supported using PC

parallel port I/O operations.

1

pac30_01

鈻?/div>

Applications

Vin1

Vin2

Vin3

ispPAC30

Dual

12-Bit

ADC

碌Controller

www.latticesemi.com

![]() LATTICE

LATTICE