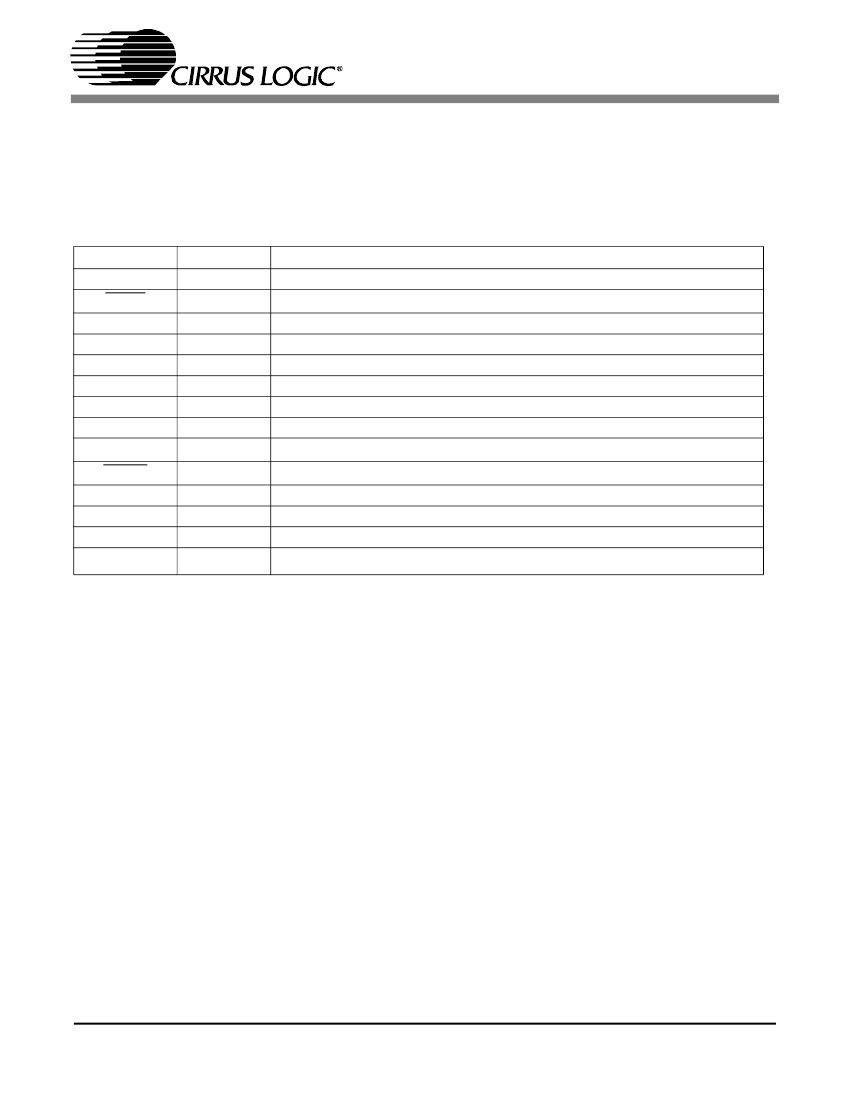

Three General Purpose outputs are provided to allow the equipment designer flexibility in configuring the

CS8416.

Fourteen signals are available to be routed to the GPOs.

State of EMPH bit in incoming stream. Same polarity as EMPHb bit.

鈮?/div>

88.1

Non-audio indicator for decoded input stream

Virtual LRCK

Fixed low Level

VDD fixed high level

F

S

X 512 (Note

13)

Table 3. GPO Pin Configurations

Notes: 13. Frequency = 25 MHz Max, duty cycle not guaranteed, target duty cycle = 50% @ F

S

= 48 kHz.

Codes 1110 to 1111 - Reserved

6.4

Interrupts

The CS8416 has a comprehensive interrupt capa-

bility. The INT pin may be set to be active low, ac-

tive high or active low with no active pull-up

transistor. This last mode is used for active low,

wired-OR hook- ups, with multiple peripherals

connected to the microcontroller interrupt input

pin.

Many conditions can cause an interrupt, as listed in

the interrupt status register descriptions. Each

source may be masked off through mask register

bits. In addition, each source may be set to rising

edge, falling edge, or level sensitive. Combined

with the option of level sensitive or edge sensitive

modes within the microcontroller, many different

configurations are possible, depending on the

needs of the equipment designer.

22

DS578PP2