CS8416

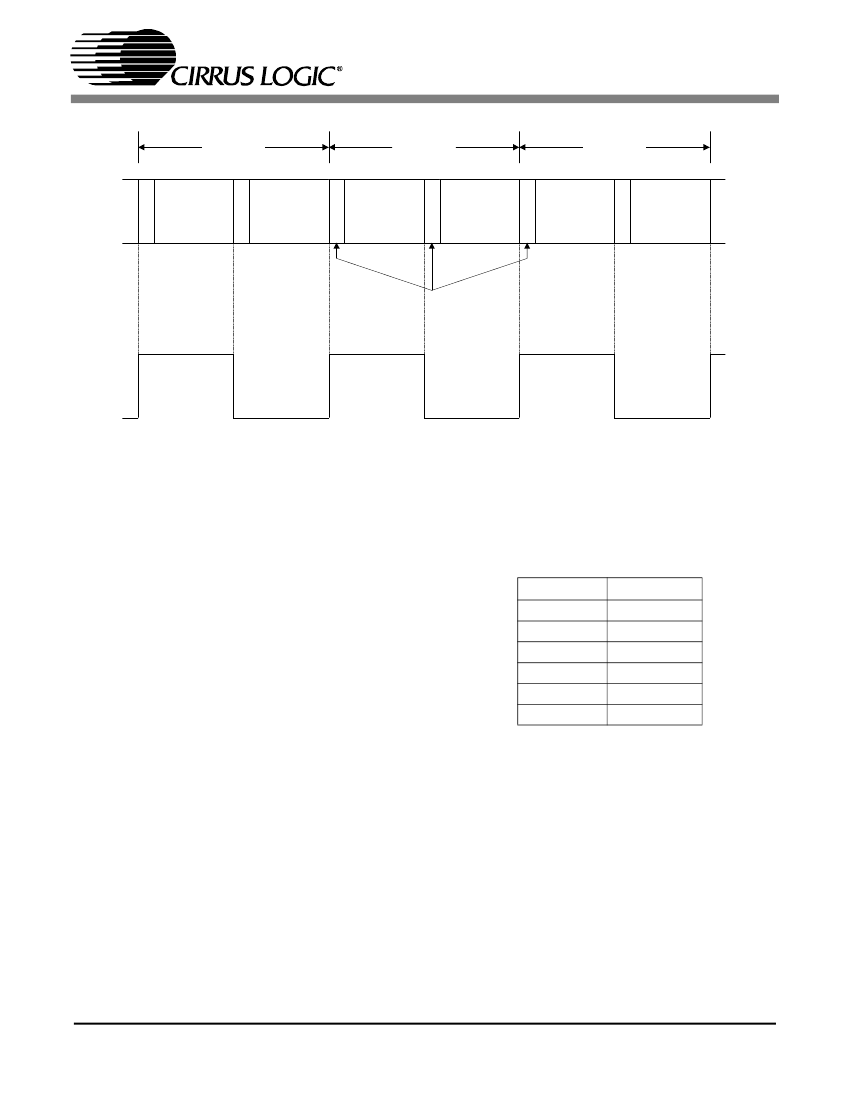

Frame 191

Frame 0

Frame 1

X

Channel A

Data

Y

Channel B

Data

Z

Channel A

Data

Y

Channel B

Data

X

Channel A

Data

Y

Channel B

Data

Preambles

OLRCK (in slave mode)

Figure 7. AES3 Data Format

If the user reads OSLIP as soon as the event trig-

gers, over a long period of time the rate of occur-

ring INT will be equal to the difference in

frequency between the input AES data and the

slave serial output LRCK. The CS8416 uses a hys-

teresis window when a slip/repeat event occurs.

The slip/repeat is triggered when an edge of OL-

RCK passes a window size from the beginning of

the Z/X preamble. Without the hysteresis window,

jitter on OLRCK with a frequency very close to Fs

could slip back and forth, causing multiple slip/re-

peat events. The CS8416 uses a hysteresis window

to ensure that only one slip/repeat happens even

with jitter on OLRCK.

master mode without the de-emphasis filter en-

gaged, the latency of the audio data will be 3

frames.

Fs (kHz)

32

44.1

48

64

96

192

Delay (ns)

96.6

78.6

74.6

60.6

50.6

TBD

Table 1. Delays by Frequency Values

4.2

AES11 Behavior

When OLRCK is configured as a master, the posi-

tive or negative edge of OLRCK (depending on the

setting of SOLRPOL in register 05h) will be within

-1.0%(1/Fs) to 1.1%(1/Fs) from the start of the pre-

amble X/Z. In master mode, the latency through the

part is dependent on the input sample frequency.

The delay through the part from the beginning of

the preamble to the active edge of OLRCK for the

various sample frequencies is given in

Table 1.

In

14

When OLRCK is configured as a slave any syn-

chronized input within +/-28%(1/Fs) from the pos-

itive or negative edge of OLRCK (depending on

the setting of SOLRPOL in register 05h) will be

treated as being sampled at the same time. Since the

CS8416 has no control of the OLRCK in slave

mode, the latency of the data through the part will

be a multiple of 1/Fs plus the delay between OL-

RCK and the preambles.

Both of these conditions are within the tolerance

range set forth in the AES11 standard.

DS578PP2