47K鈩?/div>

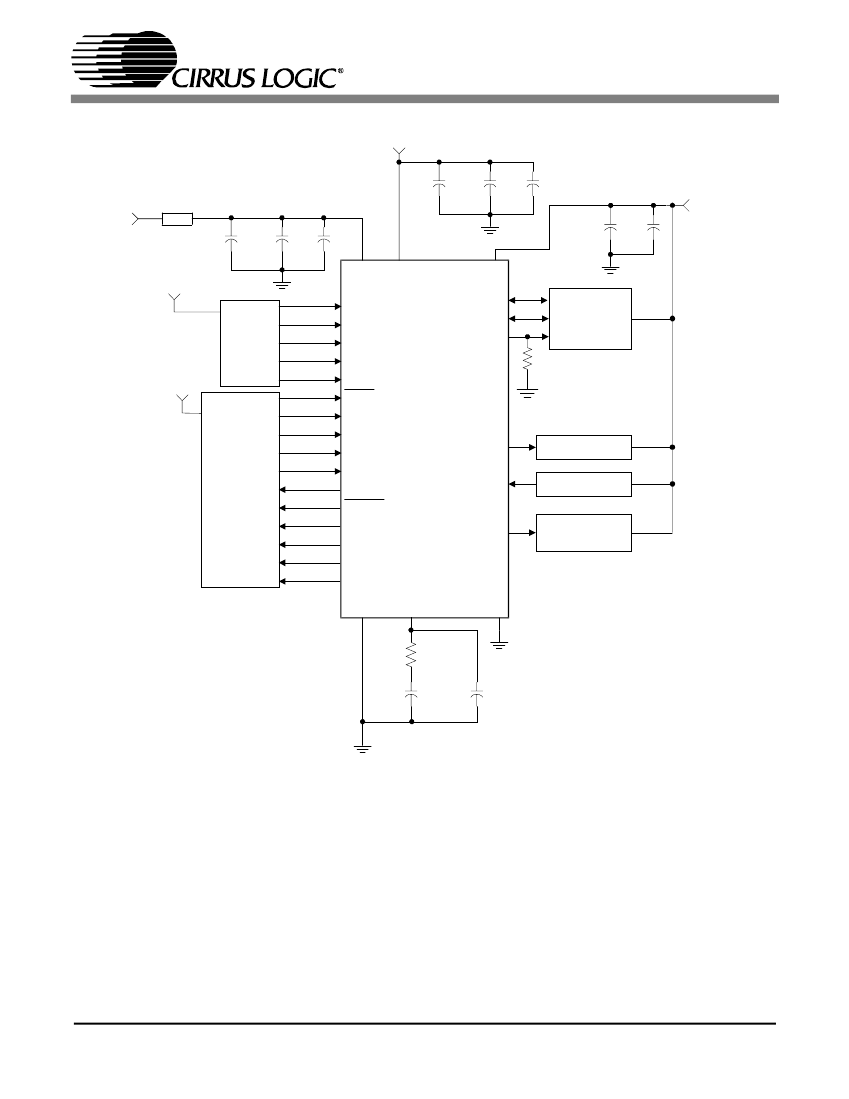

CS8416

RMCK

OMCK

Clock Control

Clock Source

External

Interface

Hardware

Control

TXSEL1

NV/RERR

*

*

96KHZ

*

RCBL

*

U

*

C

*

AUDIO

AGND

FILT

TX

DGND

Rflt

Cflt

Crip

****

*

These pins must be pulled high to VL+ or low to DGND through a 47K鈩?resistor.

**

A seperate analog supply is only necessary in applications where RMCK is used for a jitter

sensitive tast. For applications where RMCK is not used for a jitter sensitive task, connect

VA+ to VD+ via a ferrite bead. Keep decoupling capacitors between VA+ and AGND.

***

Please see section 5.1 "8:2 S/PDIF Input Multiplexer" and Appendix

A for typical input configurations and recommended input circuits.

For best jitter performance connect the filter ground directly to the AGND pin.

****

See Table 2 for PLL filter values.

Figure 6. Typical Connection Diagram - Hardware Mode

DS578PP2

11