CS8415A

SWITCHING CHARACTERISTICS - CONTROL PORT - I

2

C MODE

(Note 15, Inputs: Logic 0 = 0 V, Logic 1 = VL+; C

L

= 20 pF)

Parameter

SCL Clock Frequency

Bus Free Time Between Transmissions

Start Condition Hold Time (prior to first clock pulse)

Clock Low Time

Clock High Time

Setup Time for Repeated Start Condition

SDA Hold Time from SCL Falling

SDA Setup Time to SCL Rising

Rise Time of Both SDA and SCL Lines

Fall Time of Both SDA and SCL Lines

Setup Time for Stop Condition

Notes: 15. I

2

C protocol is supported only in 5V mode.

16. Data must be held for sufficient time to bridge the 25 ns transition time of SCL.

(Note 16)

Symbol

f

scl

t

buf

t

hdst

t

low

t

high

t

sust

t

hdd

t

sud

t

r

t

f

t

susp

Min

-

4.7

4.0

4.7

4.0

4.7

0

250

-

-

4.7

Typ

-

-

-

-

-

-

-

-

-

-

-

Max

100

-

-

-

-

-

-

-

25

25

-

Units

kHz

碌s

碌s

碌s

碌s

碌s

碌s

ns

ns

ns

碌s

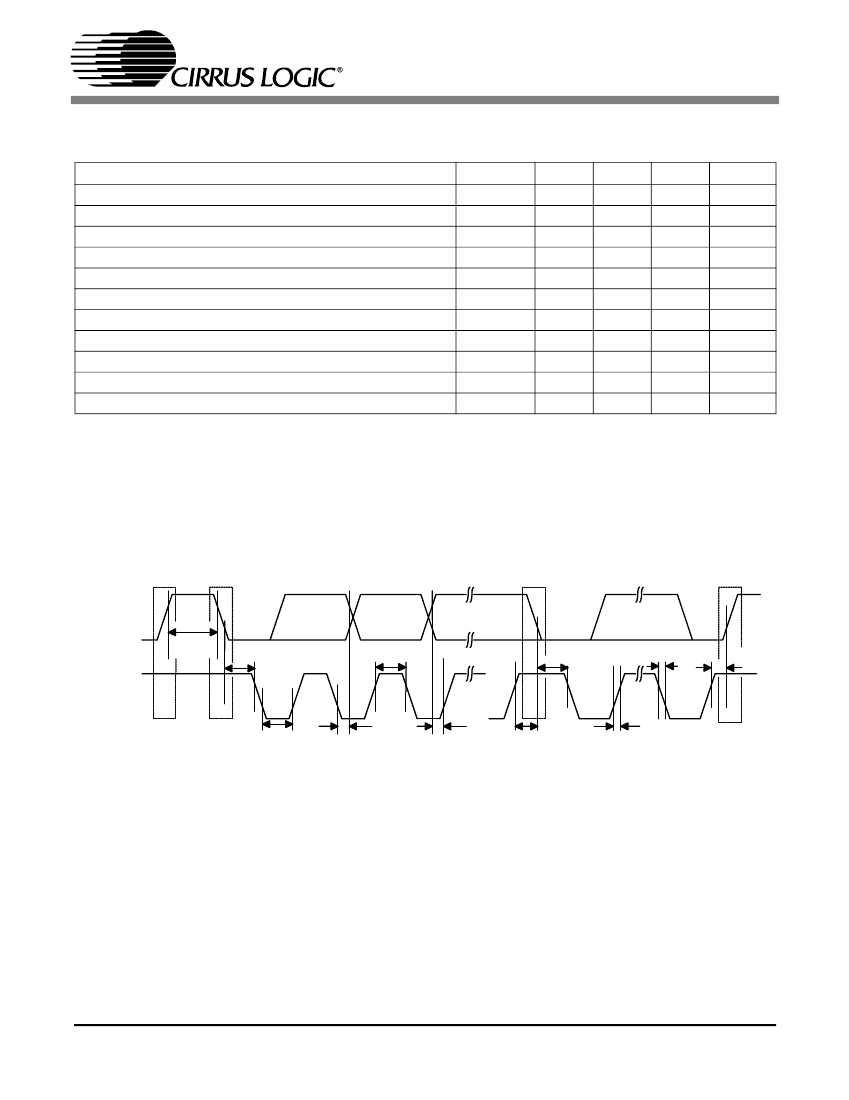

Stop

SDA

t buf

SCL

Start

Repeated

Start

Stop

t hdst

t high

t

hdst

tf

t susp

t

low

t

hdd

t sud

t sust

tr

Figure 4. I

2

C Mode timing

9